## CS184a: Computer Architecture (Structure and Organization)

Day 21: March 2, 2005 Time Multiplexing

CS184 Wint

| Benchmark Set |             |             |         |             |             |

|---------------|-------------|-------------|---------|-------------|-------------|

| • 23 N        | ИСИС с      | ircuits     |         |             |             |

|               |             | ad with C   |         |             |             |

| – ar          | ea mapp     | ea with a   | no ar   | nd Chortle  |             |

| Circuit       | Mapped LUTs | Path Length | Circuit | Mapped LUTs | Path Length |

| 5xp1          | 46          | 10          | des     | 1267        | 13          |

| 9sym          | 123         | 7           | e64     | 230         | 9           |

| 9symml        | 108         | 8           | f51m    | 45          | 17          |

| C499          | 85          | 10          | misex1  | 20          | 6           |

| C880          | 176         | 21          | misex2  | 38          | 8           |

| alu2          | 169         | 19          | rd73    | 105         | 10          |

| apexó         | 248         | 9           | rd84    | 150         | 9           |

| apex7         | 77          | 7           | rot     | 293         | 16          |

| 1.0           | 46          | 7           | sao2    | 73          | 9           |

| b9            | 101         | 9           | vg2     | 60          | 9           |

| clip          | 121         | /           |         |             |             |

|               | 367         | 13          | z4ml    | 8           | 7           |

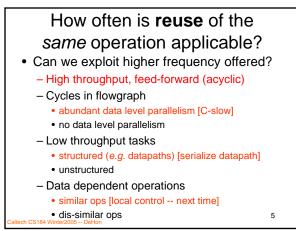

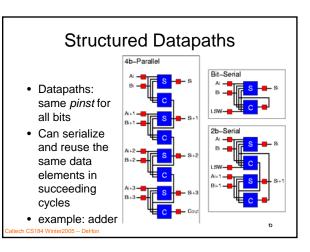

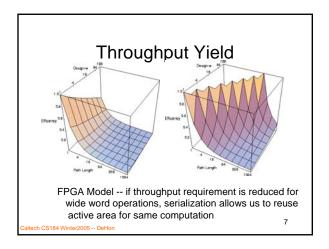

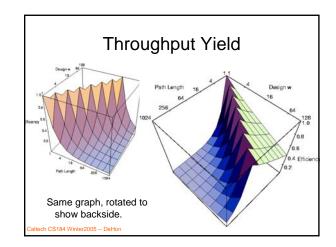

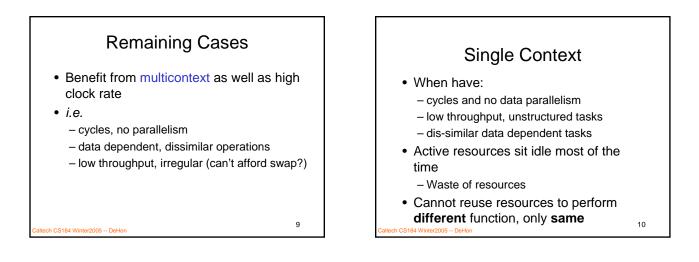

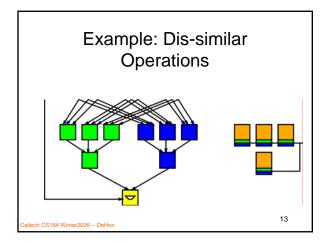

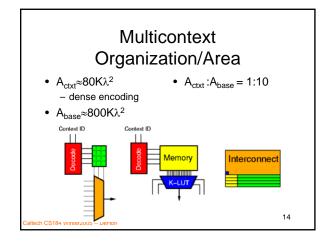

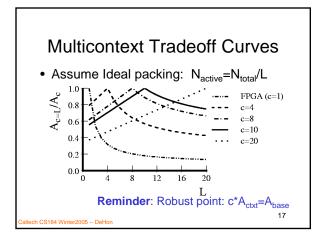

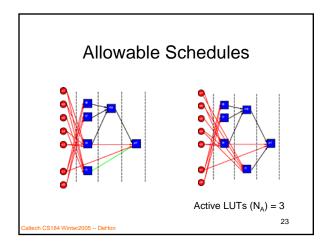

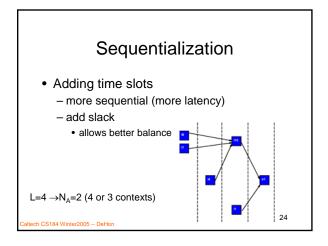

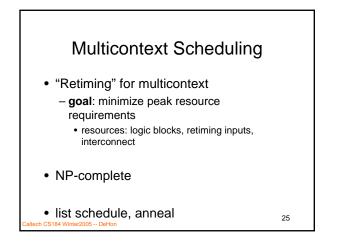

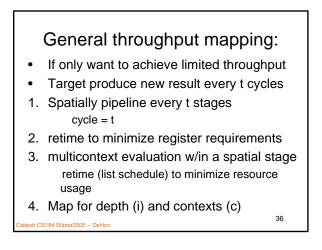

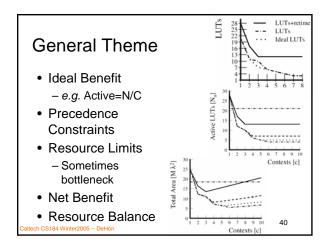

## Big Ideas [MSB Ideas] • Several cases cannot profitably reuse same logic at device cycle rate - cycles, no data parallelism - low throughput, unstructured - dis-similar data dependent computations • These cases benefit from more than one instructions/operations per active element • A<sub>ctxt</sub><< A<sub>active</sub> makes interesting - save area by sharing active among - instructions

## Big Ideas [MSB-1 Ideas]

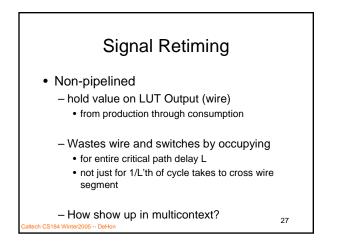

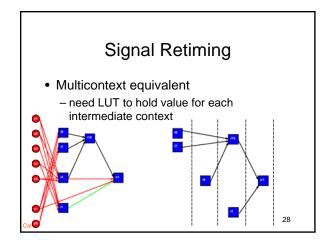

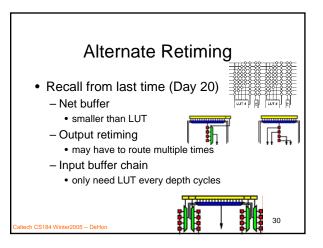

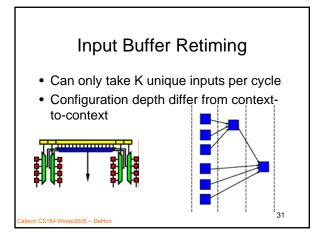

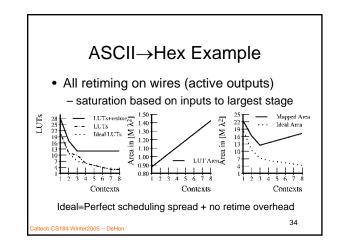

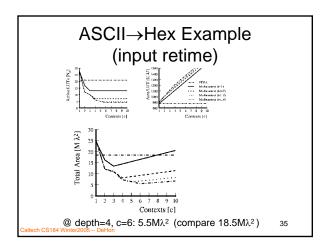

Economical retiming becomes important here to achieve active LUT reduction

- one output reg/LUT leads to early saturation

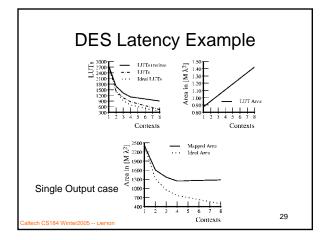

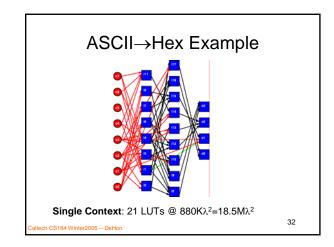

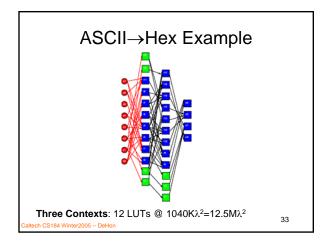

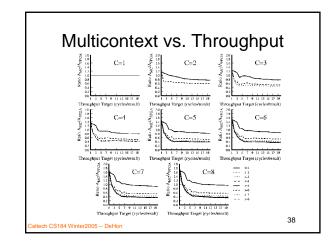

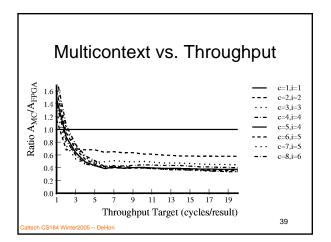

- c=4--8, I=4--6 automatically mapped designs 1/2 to 1/3 single context size

- Most FPGAs typically run in realm where multicontext is smaller

- How many for intrinsic reasons?

- How many for lack of HSRA-like register/CAD support?

ach CS184 Winter2005 -- DeHon