#### CS184a: Computer Architecture (Structure and Organization)

Day 19: February 23, 2005 Retime 1: Transformations

Caltech CS184 Winter2005 -- DeHon

#### Previously

- · Reviewed Pipelining

- basic assignments on

- Saw spatial designs efficient

- when reuse logic at maximum frequency

- · Interconnect is dominant delay

- and dominant area

- heavy call to reuse to use efficiently

Caltech CS184 Winter2005 -- DeHon

2

#### Today

Systematic transformation for retiming

preserve semantics (meaning)

Caltech CS184 Winter2005 -- DeHor

#### Motivation

Caltech CS184 Winter2005 -- DeHon

4

#### Motivation

- · FPGAs (spatial computing)

- run efficiently when all resources reused rapidly

- cycle time minimized

"Everything in the right place at the right time."

Caltech CS184 Winter2005 -- DeHon

5

#### **Motivating Questions**

- Can I build a fixed-frequency (fixed clock) programmable architecture?

- Can I always make a design run at maximum clock rate?

- How do we systematically transform any computation to

- Operate on fixed-frequency array?

- Coordinate around mandatory registers in design?

Caltech CS184 Winter2005 -- DeHon

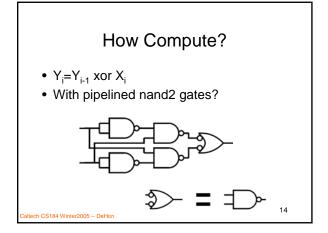

## Retiming Algorithm

altech CS184 Winter2005 -- DeHor

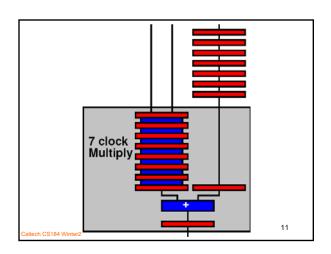

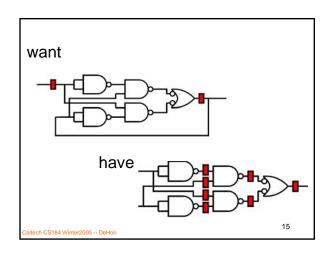

#### Task

- Move registers to:

- Preserve semantics

- Minimize path length between registers

- i.e. Make path length 1 for maximum throughput or reuse

- ...while minimizing number of registers required

Caltech CS184 Winter2005 -- DeHon

17

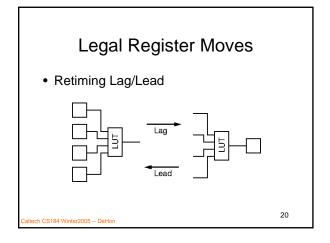

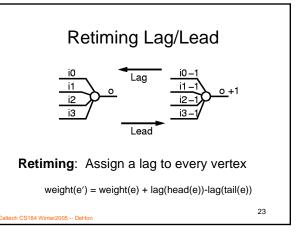

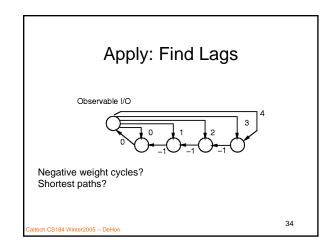

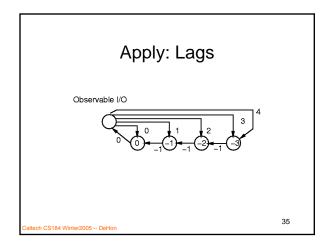

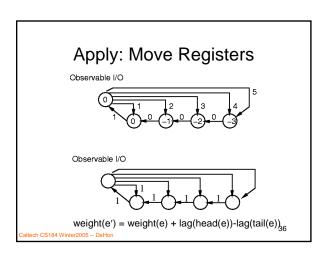

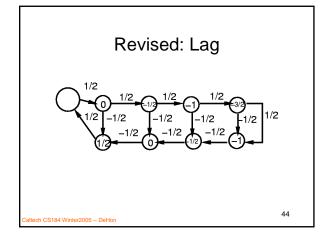

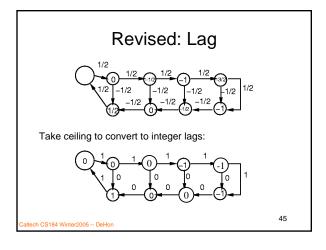

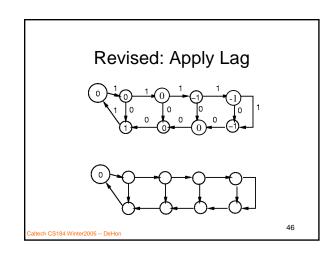

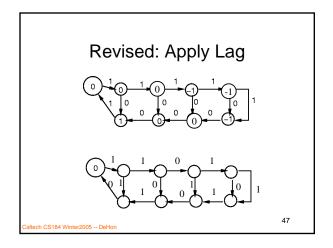

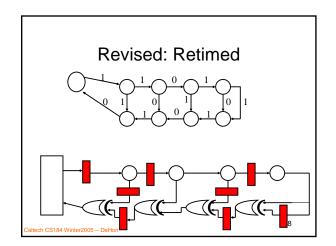

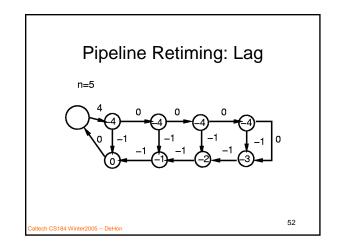

# Valid Retiming • Retiming is valid as long as: — ∀e in graph • weight(e') = weight(e) + lag(head(e))-lag(tail(e)) ≥ 0 • Assuming original circuit was a valid synchronous circuit, this guarantees: — non-negative register weights on all edges • no travel backward in time :-) — all cycles have strictly positive register counts — propagation delay on each vertex is non-negative (assumed 1 for today)

Δ

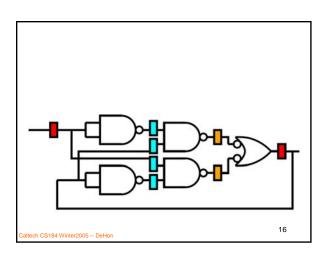

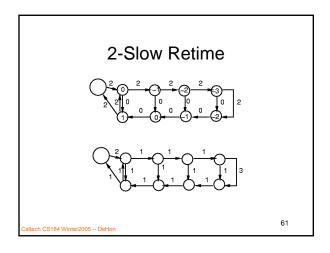

#### **Retiming Task**

- Move registers = assign lags to nodes - lags define all locally legal moves

- Preserving non-negative edge weights

- (previous slide)

- guarantees collection of lags remains consistent globally

25

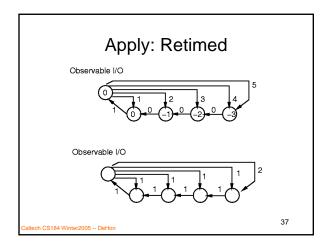

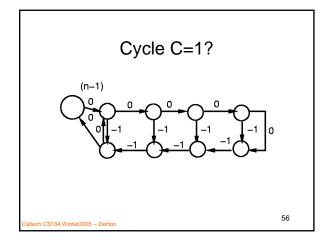

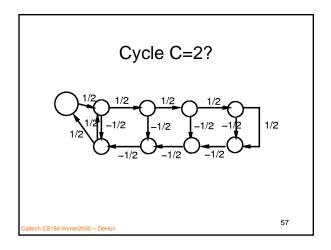

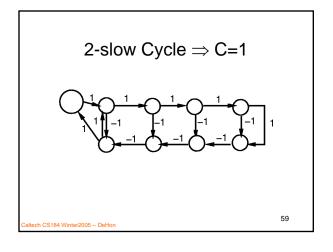

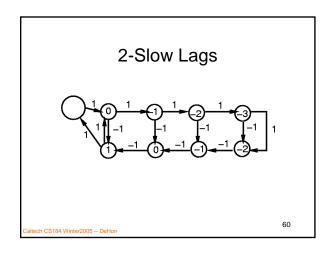

#### **Retiming Transformation**

- N.B.: unchanged by retiming

- number of registers around a cycle

- delay along a cycle

- Cycle of length P must have

- at least P/c registers on it

- to be retimeable to cycle c

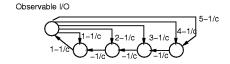

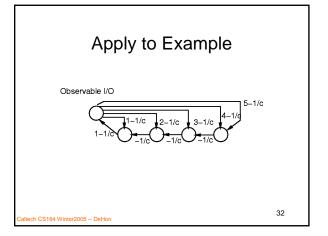

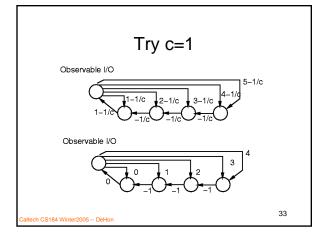

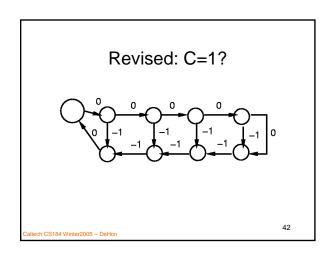

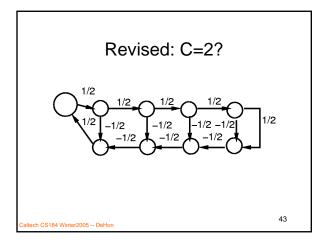

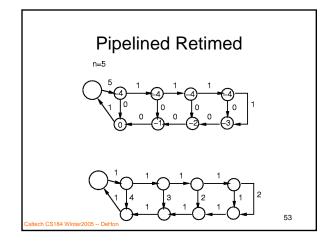

#### **Optimal Retiming**

- · There is a retiming of

- graph G

- w/ clock cycle c

- iff G-1/c has no cycles with negative edge weights

- G- $\alpha$  = subtract  $\alpha$  from each edge weight

27

29

#### 1/c Intuition

- Want to place a register every c delay units

- · Each register adds one

- Each delay subtracts 1/c

- As long as remains more positives than negatives around all cycles

- can move registers to accommodate

- Captures the regs=P/c constraints

28

#### G-1/c

#### Compute Retiming

- Lag(v) = shortest path to I/O in G-1/c

- Compute shortest paths in O(|V||E|)

- Bellman-Ford

- also use to detect negative weight cycles when c too small

#### Bellman Ford

- For I←0 to N

- $-u_i \leftarrow \infty$  (except  $u_i=0$  for IO)

- For k←0 to N

- for  $e_{i,j} \in E$

- $u_i \leftarrow \min(u_{i,u_j} + w(e_{i,j}))$

- For  $e_{i,j} \in E$  //still update  $\rightarrow$  negative cycle

- if  $u_i > u_j + w(e_{i,j})$

- cycles detected

Caltech CS184 Winter2005 -- DeHon

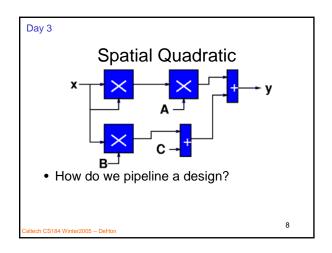

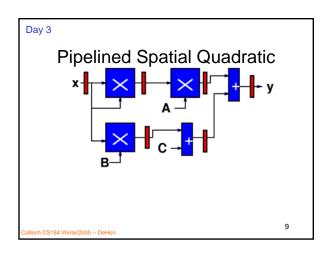

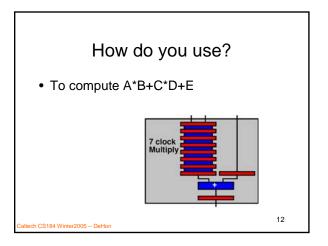

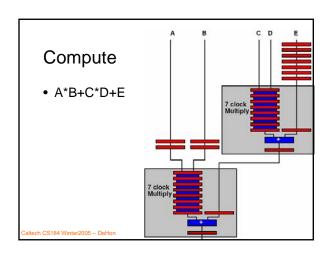

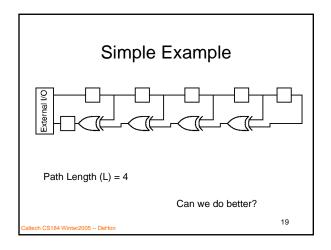

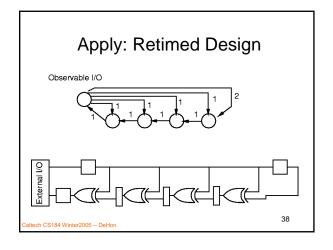

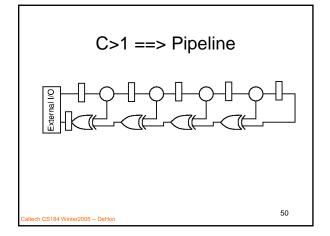

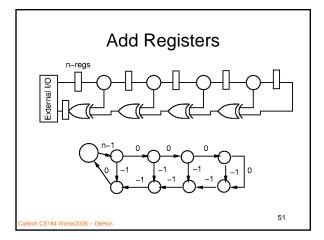

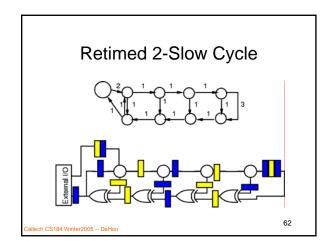

#### Pipelining

- We can use this retiming to pipeline

- Assume we have enough (infinite supply) registers at edge of circuit

- · Retime them into circuit

ch CS184 Winter2005 -- DeHon

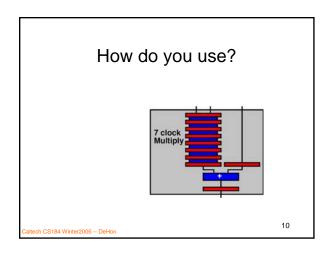

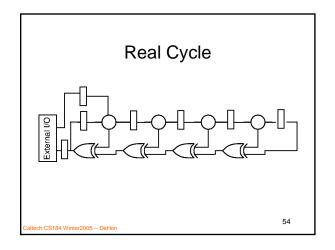

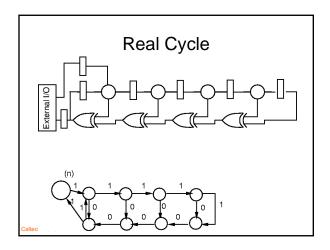

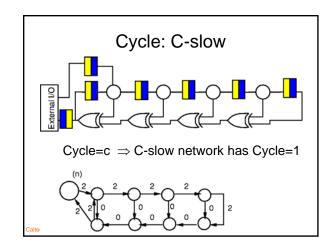

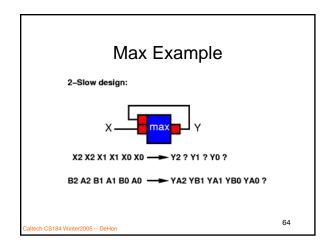

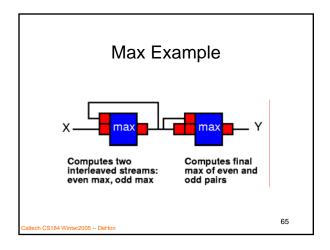

#### C-Slow applicable?

- Available parallelism

- solve C identical, independent problems

- Data-level parallelism

- e.g. process packets (blocks) separately

- e.g. independent regions in images

- Commutative operators

- e.g. max example

84 Winter2005 -- DeHon

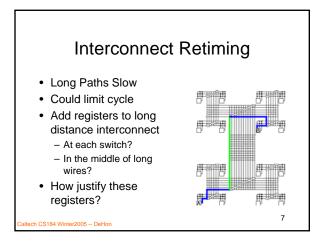

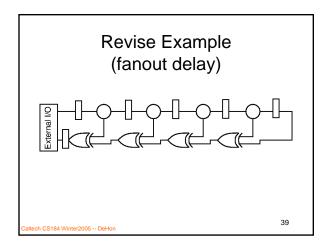

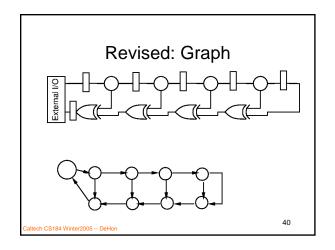

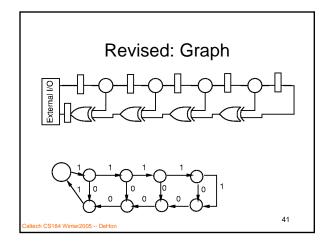

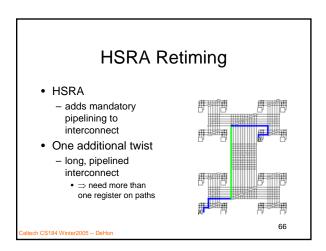

### Accommodating HSRA Interconnect Delays

- Add buffers to LUT→LUT path to match interconnect register requirements

- Retime to C=1 as before

- Buffer chains force enough registers to cover interconnect delays

Caltach CS184 Winter2005 -- DeHon

67

#

#### Big Ideas [MSB Ideas]

- Retiming transformations important to

- minimize cycles

- efficiently utilize spatial architectures

- Optimally solvable in O(|V||E|) time

- Tells us

- pipelining required

- C-slow

- where to move registers

- Can accommodate mandatory delays 69

Caltech CS184 Winter2005 -- DeHo